TSMC sẽ đưa tiến trình sản xuất chip bán dẫn 2nm vào giai đoạn thương mại hóa từ năm 2025, theo thông tin từ chuỗi cung ứng công nghệ bên Đài Loan. Điều này cho thấy kế hoạch roadmap của TSMC hiện đang được thực hiện mà không có khó khăn trở ngại nào đáng kể. Có tin đồn cho rằng TSMC đang lên kế hoạch cho một tiến trình 2nm mới, cải tiến từ tiến trình cũ để tăng sản lượng cũng như tỷ lệ chip đạt chuẩn. Dự kiến tiến trình 2nm mới của TSMC sẽ gọi là N2P, tương tự như N3 và N3P của họ hiện tại.

CEO của TSMC, tiến sĩ Wei Chungching, đã từng tuyên bố rằng ông tự tin TSMC sẽ sản xuất được chip 2nm vào năm 2025. Sau đó, phó chủ tịch phụ trách nghiên cứu, phát triển và công nghệ của TSMC, tiến sĩ Mii Yujie, đã xác nhận kế hoạch này vào năm ngoái. Tháng 1 vừa qua, tiến sĩ Wei lại đưa ra những tuyên bố mới khiến thị trường tăng thêm niềm tin vào TSMC, nói rằng tiến trình 2nm được phát triển với tốc độ nhanh hơn so với dự kiến, và sẽ đưa vào giai đoạn sản xuất thử nghiệm vào năm 2024.

Theo những nguồn tin không chính thức, chip 2nm thương mại hóa sẽ được TSMC sản xuất tại fab gia công bán dẫn của họ đặt tại thị trấn Bảo Sơn thuộc thành phố Tân Trúc, nằm ở phía Tây Bắc Đài Loan. TSMC cũng đang lên kế hoạch xây dựng Fab 20 ở Đài Chung để phục vụ gia công những chip bán dẫn trên tiến trình mới nhất.

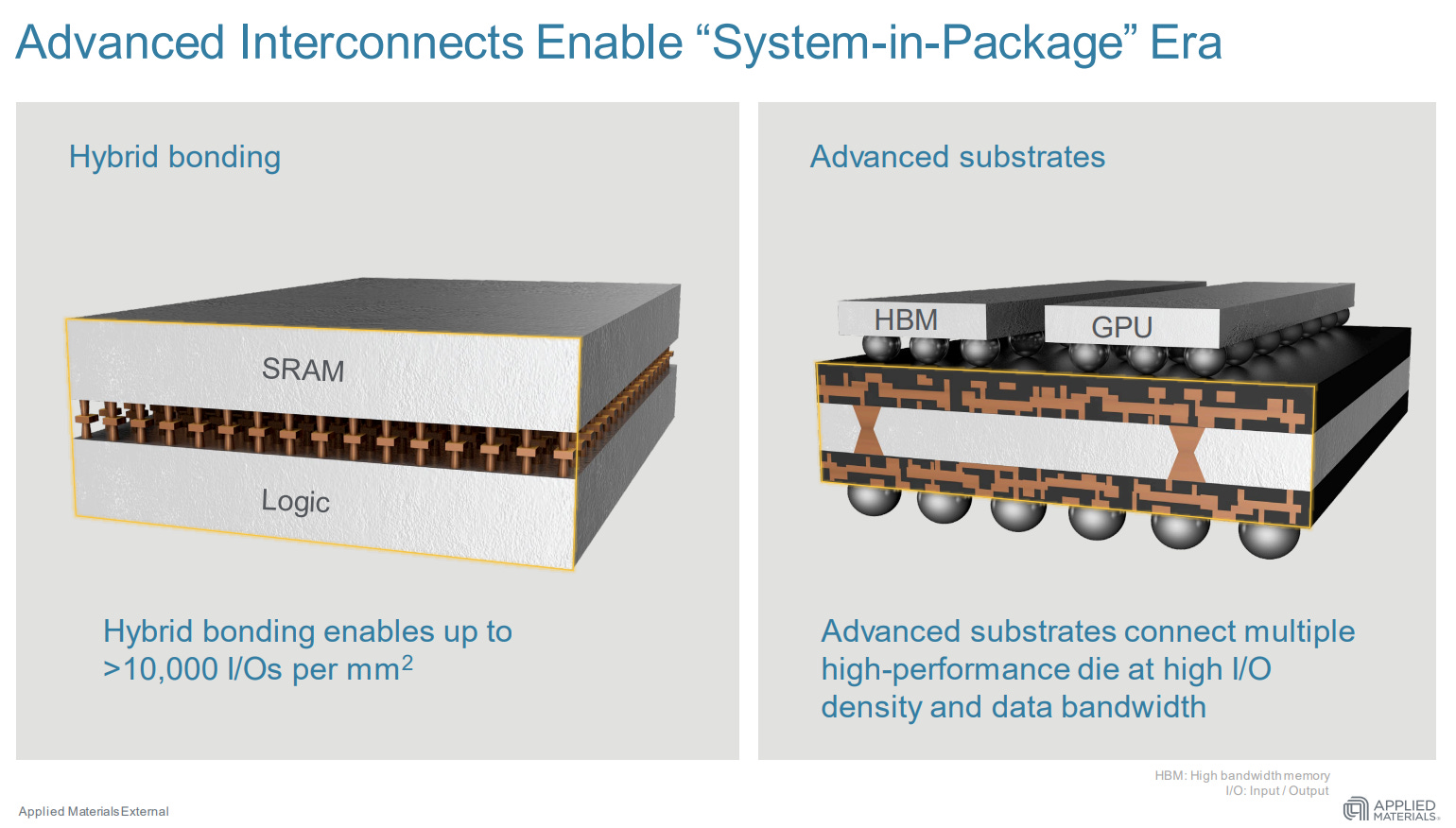

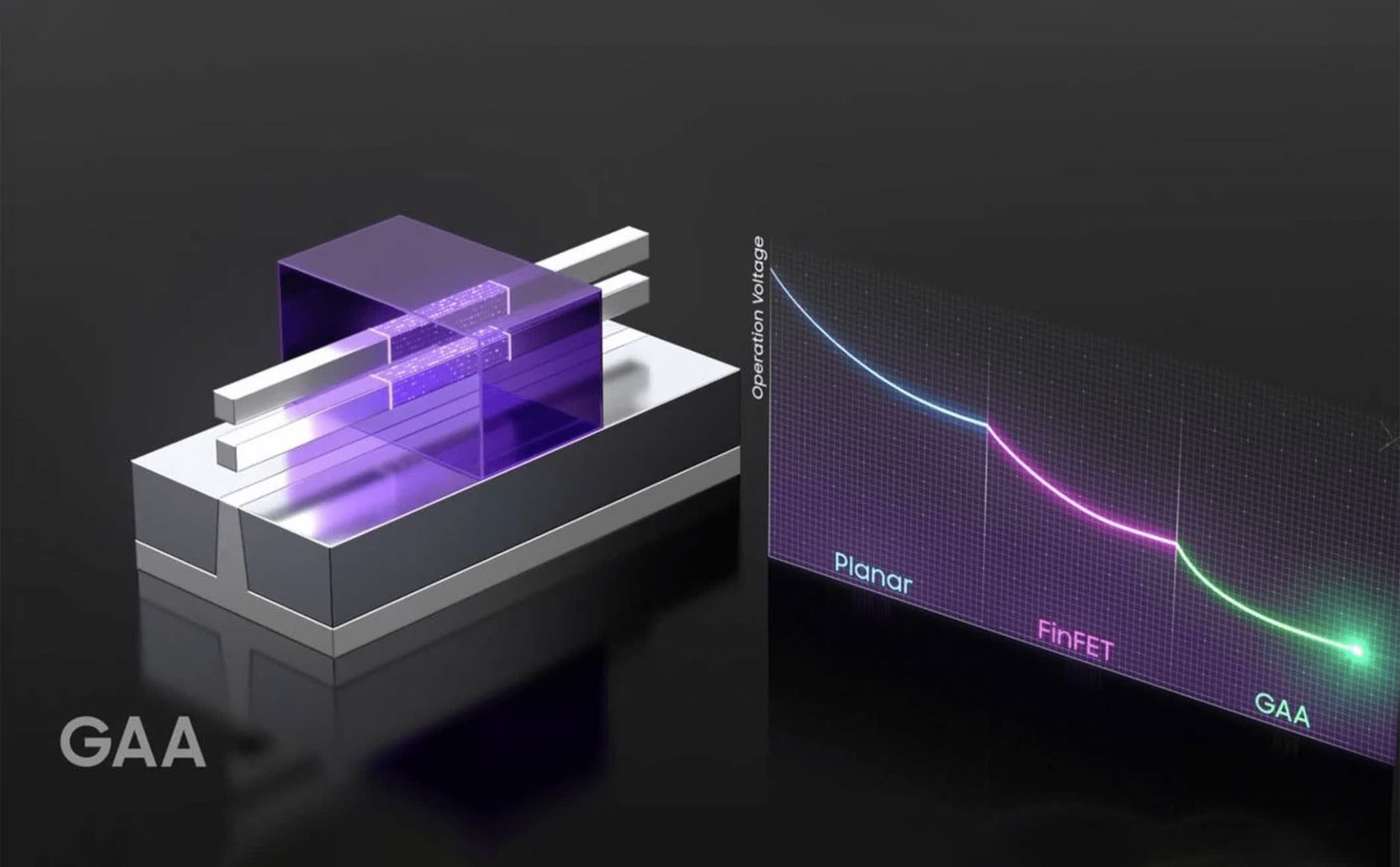

Dù TSMC chưa công bố chính thức thông tin về tiến trình N2P, giải pháp cải tiến của N2, những nguồn tin được cho là ở trong chuỗi cung ứng của TSMC nói rằng N2P sẽ ứng dụng khả năng cấp điện BSPD (back side power delivery) để tăng hiệu năng của những con chip. Thông thường một die chip xử lý sẽ phải nối dây để nhận nguồn điện cũng như nhận dữ liệu, cho phép nó tương tác với những linh kiện khác trong hệ thống. Chip càng nhỏ thì đường dẫn điện càng co lại.

Giới hạn đáng kể trong quá trình nghiên cứu chip bán dẫn tiên tiến là khoảng cách giữa các transistor chỉ bằng một phần nhỏ tiết diện của sợi tóc con người. Điều này gây khó khăn trong việc đặt các đường cấp điện trên miếng silic của chip. Một giải pháp hiệu quả là đặt các đường dây tải điện trực tiếp phía trên các transistor hoặc in thạch bản đường dẫn điện trước rồi mới in các transistor lên trên. Quy trình này được gọi là BSPD hoặc kết nối TSV (thông qua silicon vias) và cho phép nhiều chip bán dẫn, như vi xử lý và bộ nhớ, được lắp đặt chồng lên nhau để tối ưu hóa tiêu thụ điện năng. Hệ thống mạng BSPD cũng bao gồm các bước nối các wafer silicon lại với nhau để giảm trở kháng khi dòng điện đi qua các transistor.

Tuy nhiên, các chuyên gia nghiên cứu thị trường, trong đó có Morgan Stanley, dự báo doanh thu của TSMC trong quý II năm 2023 sẽ giảm từ 5 đến 9% do các nhà sản xuất điện thoại giảm đặt hàng chip SoC. Tuy nhiên, trong cả năm, doanh thu của TSMC sẽ không bị ảnh hưởng nhiều vì Apple đã chấp nhận mức giá tăng 3% cho mỗi wafer silicon gia công trên tiến trình N3, dự kiến sẽ được sử dụng để sản xuất chip cho iPhone 15 Pro ra mắt vào cuối năm nay.